사람의 손톱보다 작고 종이만큼 얇은 반도체 칩에는 미세하고 수많은 층(layer)이 존재합니다. 마치 고층 빌딩처럼 높고 견고하게 쌓여 복잡한 구조를 이루고 있는데요.

이러한 구조를 형성하기 위해서는 반도체의 원재료가 되는 단결정 실리콘(Si) 웨이퍼 위에 단계적으로 박막을 입히고 회로를 그려 넣는 포토공정을 거쳐 불필요한 부분을 선택적으로 제거하는 식각공정과 세정하는 과정을 여러 번 반복하게 됩니다.

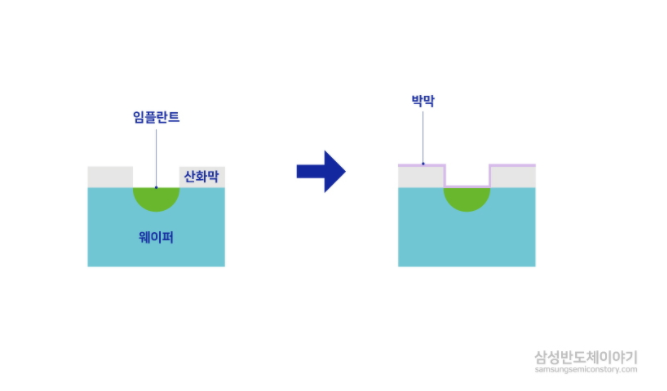

이때 회로 간의 구분과 연결, 보호 역할을 하는 얇은 막을 박막(Thin film)이라고 합니다. 이번 시간에는 이런 박막을 만드는 증착공정과 반도체가 전기적인 특성을 갖도록 만드는 일련의 과정에 대해 살펴보겠습니다.

웨이퍼에 얇은 옷을 입히는 증착공정(deposition)

사전적 의미로 ‘박막(thin film)’이란 단순한 기계 가공으로는 실현 불가능한 1마이크로미터(μm, 100만 분의 1미터) 이하의 얇은 막을 뜻합니다. 웨이퍼 위에 원하는 분자 또는 원자 단위의 박막을 입히는 일련의 과정을 증착(Deposition)이라고 하는데요. 두께가 워낙 얇기 때문에 웨이퍼 위에 균일하게 박막을 형성하기 위해서는 정교하고 세밀한 기술력을 필요로 하죠.

증착의 방법은 크게 두 가지로 나뉘는데요. 물리적 기상증착방법(PVD, Physical Vapor Deposition)과 화학적 기상증착방법(CVD, Chemical Vapor Deposition)입니다.

물리적 기상증착방법(PVD)는 금속 박막의 증착에 주로 사용되며 화학반응이 수반되지는 않습니다. 한편 화학적 기상증착방법(CVD)는 가스의 화학 반응으로 형성된 입자들을 외부 에너지가 부여된 수증기 형태로 쏘아 증착 시키는 방법인데요. 도체, 부도체, 반도체의 박막증착에 모두 사용될 수 있는 기술입니다.

현재 반도체 공정에서는 화학적 기상증착방법(CVD)를 주로 사용하고 있습니다. 화학적 기상증착방법(CVD)은 사용하는 외부 에너지에 따라 열 CVD, 플라즈마 CVD, 광 CVD로 세분화되는데요. 특히 플라즈마 CVD는 저온에서 형성이 가능하고 두께 균일도를 조절할 수 있으며 대량 처리가 가능하다는 장점 때문에 가장 많이 이용되고 있습니다.

증착공정을 통해 형성된 박막은 크게 회로들 간 전기적인 신호를 연결해주는 금속막(전도)층과 내부 연결층을 전기적으로 분리하거나 오염원으로부터 차단시켜주는 절연막층으로 구분됩니다.

웨이퍼를 반도체로 만드는 이온주입공정(Ion Implantation)

이때 반도체가 전기적인 성질을 가지게 하는 공정이 수반되어야 합니다. 전기가 통하는 도체와, 통하지 않는 부도체의 성질을 동시에 가진 반도체에서 이온주입공정(Ion Implantation)은 실리콘 웨이퍼에 반도체의 생명을 불어넣는 작업입니다. 순수한 반도체는 규소로 되어있어 전기가 통하지 않으나 불순물을 넣어줘 전류를 흐르게 하는 전도성을 갖게 되는 것이죠.

이때 불순물을 이온(Ion)이라고 하는데, 이온을 미세한 가스입자로 만들어 원하는 깊이만큼 웨이퍼 전면에 균일하게 넣어줍니다. 여기서 불순물로는 15족 원소 인(P), 비소(As), 13족 원소 붕소(B) 등을 사용하게 되는데요. 15족 원소를 주입하면 n형 반도체가 되고, 13족 원소를 주입하면 p형 반도체가 됩니다.

박막을 얼마나 얇고 균일하게 입혔느냐가 반도체의 품질을 좌우할 정도로 증착공정은 중요합니다. 미래에는 머리카락 수백만 분의 1 크기의 반도체 회로 구조가 전기적 성격을 가지도록 하기 위해, 더욱 얇고 균일하게 박막이 형성되도록 하는 증착기술이 필요할 것입니다.

다음 시간에는 산화, 포토, 식각, 증착공정을 통해 만든 소자들을 상호 연결하여 회로의 기능을 갖도록 하는 과정인 금속 배선 공정에 대해 알아보겠습니다.

'Finance Investment > 반도체와반도체장비' 카테고리의 다른 글

| [반도체] 8대 공정 8탄, 완벽한 반도체로 태어나기 위한 첫 번째 테스트 ‘EDS공정’ (0) | 2021.01.04 |

|---|---|

| [반도체] 8대 공정 7탄, 전기가 통하는 길을 만드는 ‘금속 배선 공정’ (0) | 2021.01.04 |

| [반도체] 8대 공정 5탄, 반도체 회로패턴의 완성 '식각 공정' (0) | 2021.01.04 |

| [반도체] 8대 공정 4탄, 웨이퍼에 회로를 그려 넣는 포토공정 (0) | 2021.01.04 |

| [반도체] 8대 공정 3탄, 전자산업의 혁명! 집적회로 (0) | 2021.01.04 |